I attended the seminar in Sacramento and i urge you to do the same, as you not only get vital information for developing

with the AVR and FPSLIC but also a free STK300 , a 30$ discount voucher for the purchase of an STK 500 (so you can get an STK 500 for 49$) and a nice FPSLIC t-shirt :-)

On top of that you get to meet the Atmel guys (and girls) up-close and personal and they will answer all your development questions.

(From left to right Wendy Lockhart, Joel Rosenberg, Bard Pedersen and Detlef Schick)

Check this link for more details on dates and locations.

Here is a brief overview of what we have been told. First the AVR stuff

For those of you who are not familiar with the AVR family you will get an overview of the architecture, development tools,

code examples and comparisons for code size between AVR and other mcu's.

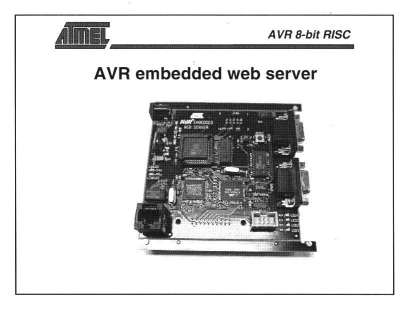

For me the most interesting part was one of the upcoming reference designs which include an AVR embeded web server starter kit.

It will provide a low level Ethernet interface, tcp/ip stack, HTTP, FTP ,e-mail support and a file system for storing web pages and data. The web "board" is at production and expected to be availiable end of 1st Q 2001.

The other intresting part to existing AVR users is the next generation of AVR controllers.

There are going to be "shrunk" versions of the existing parts, with reduced power consumption and improved instruction set.

Clock speed is going to double (@5V) and with the added instructions for integer and and fractional multiplication of both signed and unsigned numbers the AVR will be able to replace some DSP designs.

The new devices will include some new peripherals like

Two wire interface

USART's

On chip voltage reference

Brown out detector

and Reset flags

The new silicon will also have improvents on existing peripherals including an update external memory interface, which will allow the easier intergration of memory maped peripherals.

On the analog part and I/O the new parts will have

Improved Power-On reset

Enhanced Brown-Out detector

Enhanced A/D converter

and internal voltage references

For the I/O all pins will be able to sink and source 20mA and the noise emissions will be reduced