About the Workshop ... Program Schedule ... Abstract ... Speakers

Event report and photographs

|

|

Organized by

VLSI Society of India |

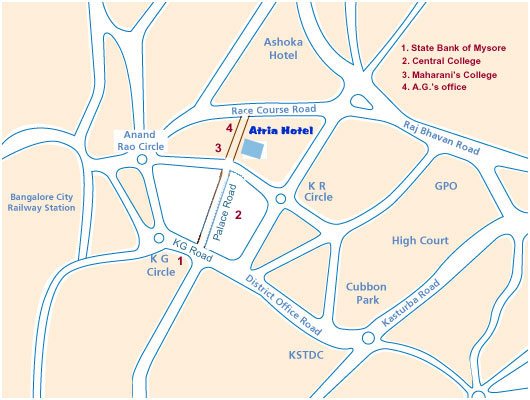

Second International Workshop on Interconnect Design and Variability December 13-14, 2007, Bangalore, India Venue: Room Conclave - The Atria Hotel

P.B. No. 5089, No. 1, Palace Road, Bangalore - 560001

E-mail: atriahotel@yahoo.com, atriahotel@rediffmail.com www.atriahotel.com |

||||||||||||||||||

|

Sponsored by | ||||||||||||||||||||

|

Cadence Design Systems |

IEEE Circuits and Systems Society Bangalore Chapter |

|||||||||||||||||||

|

|

Scope of the Workshop |

|||||||||||||||||||

|

General Co-Chairs: Nagaraj, N.S. Texas Instruments Inc., Dallas C.P. Ravikumar, Texas Instruments India

Speakers: Juan C. Rey, Mentor Graphics Corporation Srinivas Mandavilli, Mentor Graphics India Kazuya Masu, Tokyo Institute of Technology Ersed Ackasu, OEA International, Inc. Noel Menezes, Intel Corporation Sachin Sapatnekar, University of Minnesota Tom Williams, Synopsys Vish Sundararaman, Texas Instruments Inc., Dallas Steffen Rochel, Blaze DFM Inc., Nishath Verghese and Atul Sharan, Cadence Design Sys. Nagaraj, N.S., Texas Instruments Inc., Dallas Palkesh Jain and Gautam Kapila Texas Instruments India Madhav P. Desai, IIT Bombay Vani Prasad, Freescale Semiconductor Vidyasagar Ganesan, AMD

|

Interconnect scaling and variability are two difficult challenges in sub-100nm technology nodes. This workshop aims at addressing the following topics.

Latest advances in interconnect modeling and design innovations to continue performance scaling in sub-100nm technologies: v Technology scaling trends v New process realities in sub-100nm technologies v Alternative interconnect methods v Interconnect analysis algorithms v Design and Architecture methods to mitigate RC scaling

In depth review of the latest advances in variability in sub-100nm technologies: v Device and interconnect process variations v Algorithms related to statistical analysis of performance and leakage v Practical approaches to address variability v Variation tolerant design methods |

|||||||||||||||||||

|

Workshop history: The First IDV Workshop 2006 was held at IISc, Bangalore, during December 28-29, and was attended by 70 participants. http://vlsi-india.org/vsi/activities/idv_dec06_blr/index.shtml |

Targeted Audience: The workshop will be useful to professionals as well as faculty and students who are looking for research topics. |

|||||||||||||||||||

|

Download announcement with registration form PDF 410KB.

Please also register online at http://vlsi-india.org/vsi/activities/reg.shtml apart from sending the filled hardcopy of registration form.

|

||||||||||||||||||||